733003 אביב תשע"ו, סמל

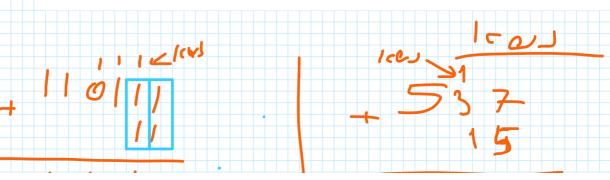

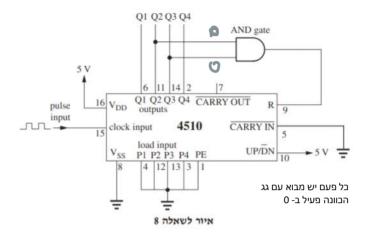

באיור לשאלה 8 מתואר מונה עשרוני 4510 . הנח שבזמן t = 0 המונה מאופס.

א. בנספח לשאלה 8 נתונים דפי המפרט של המונה. הסבר בצורה קצרה ותמציתית את פעולתם

ב. התייחס לצורת החיבור כפי שמופיע באיור לשאלה וקבע את המחזוריות של המונה (מודולו) נמק קביעתך.

## PIN DESCRIPTIONS

### INPUTS

P1, P2, P3, P4 Preset Inputs, Pins 4, 12, 13, 3) — Data on these inputs is loaded into the counter when PE is taken

Carry In (Pin 5) — Active—low input used when cascading stages. Usually connected to Carry Out of the previous stage. While high, clock is inhibited.

Clock, (Pin 15) - BCD data is incremented or decremented, depending on the direction of count, on the positive transition of this signal.

## **OUTPUTS**

45

Q1, Q2, Q3, Q4, BCD outputs (Pins 6, 11, 14, 2) - BCD data is present on these outputs with Q1 corresponding to the least significant bit.

Carry Out, (Pin 7) - Used when cascading stages, this pin is usually connected to Carry In of the next stage. This

synchronous output is active low and may also be used to indicate terminal count.

### CONTROLS

PF Preset Enable (Pin 1) — Asynchronously loads data on the Preset Inputs. This pin is active high and will inhibit the clock when high.

R, Reset, (Pin 9) — Asynchronously resets the Q outputs to a low state. This pin is active high and will inhibit the clock

Up/Down. (Pin 10) — Controls the direction of count: high for up count, low for down count.

# SUPPLY PINS

VSS, Negative Supply Voltage, (Pin 8) - This pin is usually connected to ground.

VDD, Positive Supply Voltage, (Pin 16) — This pin is connected to a positive supply voltage ranging from 3.0 Vdc to 18.0 Vdc.